# Technologie des circuits logiques

Câblage des entrées sorties Sortie standard Sortie à collecteur ouvert Sortie 3 états

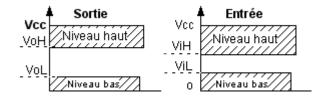

# Niveaux logiques sur les entrées.

Pour définir l'état d'une entrée, il faut mettre son potentiel à un niveau proche de Vcc pour un état haut, et proche de 0 Volt pour un niveau bas.

# Exemple de la mise à 1 d'une entrée

#### Liaison directe à Vcc

Le potentiel de l'entrée est égal à Vcc

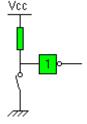

# Liaison par une résistance de rappel

La chute de tension dans la résistance est négligeable, le potentiel de l'entrée est proche de Vcc

## Entrée avec un contact

Par défaut, l'entrée est reliée à Vcc par la résistance, en cas de fermeture du contact, la tension passe à 0 Volt

Nb: Une entrée ne doit pas rester non connectée (en l'air). Sinon son état est indéterminé.

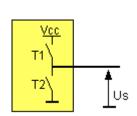

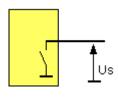

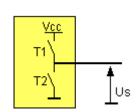

# Sortie logique standard

Une sortie logique standard est soit à l'état haut, soit à l'état bas. Le potentiel de la sortie est défini par l'état des transistors internes du circuit logique.

Pour simplifier, de simples contacts sont représentés sur le schéma.

Soit T1 est fermé, la tension de sortie Us = Vcc Soit T2 est fermé, la tension de sortie Us = 0 V

Nb : 2 sorties ne doivent pas être connectées l'une à l'autre

#### Sortie à collecteur ouvert

Dans une sortie logique à collecteur ouvert, il existe un seul transistor T2.

Le symbole d'une telle sortie est le suivant

Soit T2 est fermé, la tension de sortie Us = 0 V

Soit T2 est ouvert, aucun potentiel n'est défini sur la sortie qui est dite en haute impédance (déconnectée)

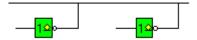

### Utilisation

Contrairement à une sortie standard, il est possible de relier plusieurs sorties sans risque de conflit.

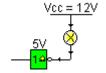

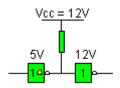

Cette sortie permet de piloter un charge avec une tension supérieure à la tension d'alimentation du circuit.

Cette sortie permet de changer de tension.

Dans le cas présent, on passe d'une logique OV / 5V à une logique OV / 12V

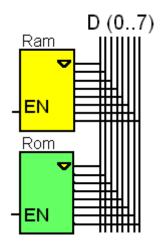

#### Sortie à trois états

Dans une logique à trois états, il est possible de bloquer simultanément les deux transistors de sortie.

Soit la sortie est à l'état haut Soit la sortie est à l'état bas Soit la sortie est en haute impédance (T1 et T2 ouverts) Le symbole d'une telle sortie est le suivant

Une entrée est dédiée à la mise en haute impédance du circuit

Ce type de circuit est utilisé pour connecter simultanément plusieurs circuits sur un même bus, un seul des circuits est connecté à un instant, les autres sont en haute impédance pour éviter les conflits. C'est le cas dans les microsystèmes avec le bus de données sur lequel sont raccordés de nombreux circuits (RAM, ROM ...)

Auteur: Alain Charbonnel